在竞争激烈的全球移动、消费类和汽车电子系统市场中,低功耗、高性能以及高可靠性是产品获得成功至关重要的因素。为了管理这些冲突性的需求,设计团队需要面面俱到地考虑多种选项,例如,需要采用高级工艺技术节点,尤其是基于FinFET的器件。这些高级技术节点让芯片不仅能在更低功耗下以更快的速度运行,同时还可在相同尺寸的芯片中集成更多功能。但是,在这些工艺节点上,由于器件的物理特性、尺寸和形状以及互联等因素,在进行功耗、噪声和可靠性签核时会遇到严重的问题。

十多年来,Ansys® RedHawk-SC™一直都是业界电源噪声和可靠性分析签核的标准解决方案,其已成为各家代工厂基准流程中不可或缺的一部分。RedHawk-SC提供优异的容量、准确度及仿真覆盖特性,能够全面满足亚7nm设计,尤其是那些需要使用FinFET器件的设计需求,因而无论是上述所列的电源噪声还是可靠性仿真问题,都能游刃有余地应对解决。本白皮书将对影响电源/信号完整性及IC可靠性的各个方面进行探讨,同时还将介绍如何运用Ansys RedHawk-SC高效率地分析和解决这些挑战。本文为白皮书节选,完整内容可在文末下载。

Ansys RedHawk-SC

凭借可扩展的架构、业界一流的引擎以及先进的建模功能,Ansys RedHawk-SC堪称率先在业界通过代工厂认证的全芯片电源噪声与可靠性签核解决方案。RedHawk-SC可充分满足高级亚7nm器件的需求,如FinFET和采用硅片直通孔 (TSV)封装技术的2.5D/3D结构需求,从而能进一步扩展上述功能。

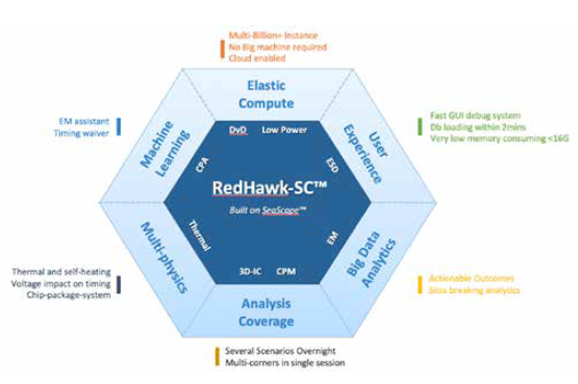

图1:Ansys RedHawk-SC平台

RedHawk-SC仿真环境能实现IP、内存和RTL级到芯片级SoC(其中包括封装和电路板)的电源噪声完整性和可靠性。IP和内存设计人员不仅能使用Ansys Totem™来验证设计,而且还可创建能在SoC级使用的紧凑型模型,从而确认集成的正确性,并评估封装和全芯片噪声对IP的影响。

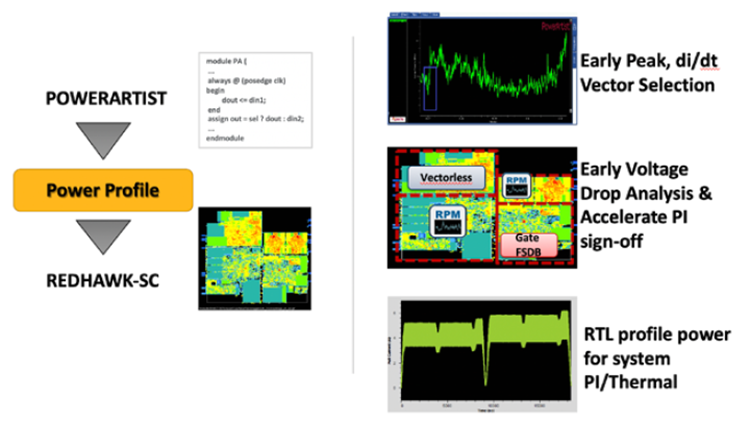

RedHawk-SC可提供综合全面的RTL2Silicon方法,它利用Ansys PowerArtist™ Design为Power RTL仿真提供的数据来扩大SoC电源噪声仿真的签核覆盖范围。对于采用高级工艺技术的设计而言,更广泛的RTL覆盖范围以及考虑温度、封装和电路板影响非常重要。

高容量、高性能

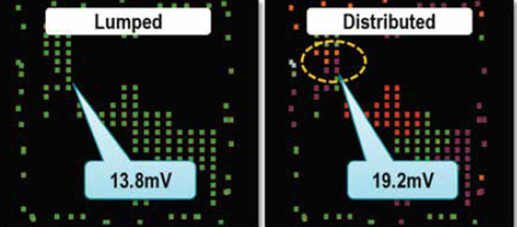

为了满足在高级工艺节点中实施大型SoC设计的准确性和签核要求,需要完整地对整个SoC和封装/PCB模型进行仿真。如果不采用适当的方法来管理这些大型仿真,那么容量和周转时间都将激增。电流在整个模块边界上流动,并穿过片上/封装电源以及接地互联点,而分层建模方法的能力非常有限,无法对这种随时间变化的电流进行建模。因此,来自分层模型的预定义电流特性,不能准确地反映芯片的实际工作状况。

经过芯片验证的签核精确度

Ansys RedHawk-SC具备业界领先晶圆厂提供的IR/DvD、EM和ESD完整性签核认证,可用于FinFET。

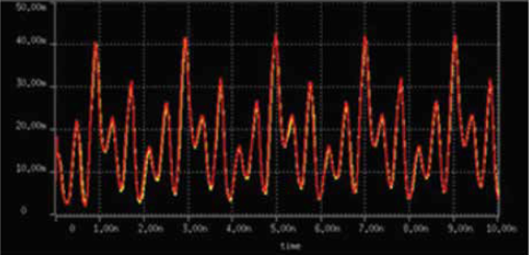

图2:准确度:SPICE与APL

RedHawk-SC可使用APL和定制宏模型 (CMM)整合器件级RC寄生效应和开关电流波形,以实现皮秒级分辨率的全芯片瞬态仿真。这些增强型模型能满足当今复杂设计中不断发展的精确度和覆盖范围需求。图2将晶体管级的SPICE仿真波形与相应的Ansys RedHawk-SC仿真(采用APL模型)进行了对比。

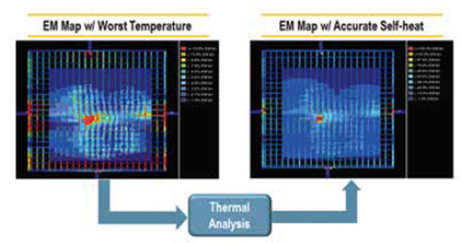

实现FinFET迁移

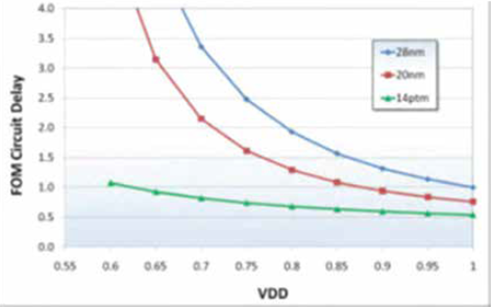

将设计迁移到FinFET结构,能在不影响待机电流的情况下,充分发挥较低动态功耗的优势。但是,FinFET的更低供电电压和较高的驱动强度会分别降低噪声容限,增大瞬态噪声。此外,FinFET的局部发热特性会升高温度,进而带来功耗/信号完整性和EM可靠性问题。另外,电路设计限制和FinFET设计中更高的电流强度会导致ESD问题,从而进一步影响可靠性。

图3:FinFET中降低工作电压的优势(资料来源:ARM公司RobAitken)

如今,在典型的高性能低功耗SoC中,有100多个电压岛、复杂的时钟和电源门级电路以及几十个IP已不足为奇,而且每个IP都会在不同的时钟和电源域中工作。所有这些因素都要求我们必须对动态压降进行准确地估算,因此,需要在实际设计工作环境中精确预测多种模式以及场景中的电流,并对动态压降进行验证,更为重要的是,需要了解压降和电源噪声对时钟和关键网络的影响。

Ansys RedHawk-SC 芯片封装分析 (RedHawk-CPA)

RedHawk-SC包含了各种经过Ansys Totem详细仿真的IP模型。此外,当今低功耗、高性能SoC的准确签核需要包含IP模型和封装/PCB寄生参数。

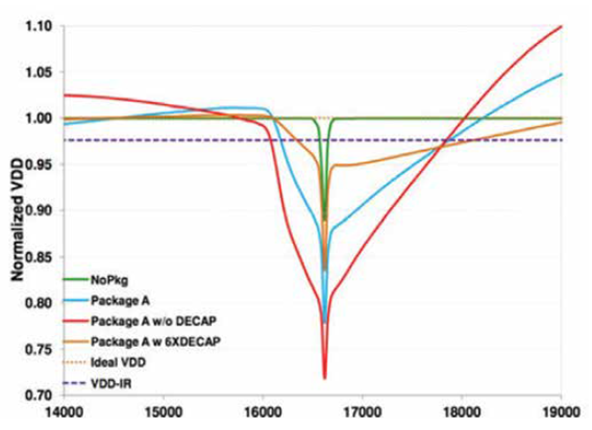

图4:封装寄生效应与解耦对芯片电源噪声的影响

RedHawk-SC提供的集成型芯片-封装协同分析解决方案Ansys RedHawk-CPA,可准确地分析封装寄生参数对动态压降的影响。对于使用高级工艺技术实现的设计,尤其是那些采用FinFET器件实现的设计,进行电源分析时应全面考虑封装中的电流、通过焊点的电流以及芯片内部的电流。该电流可通过一个时间实例到另一个时间实例的供电电压和互联阻抗变化进行调制。对于确保仿真结果的有效性和准确性而言,该因素和其它因素都至关重要。

先进的可靠性签核

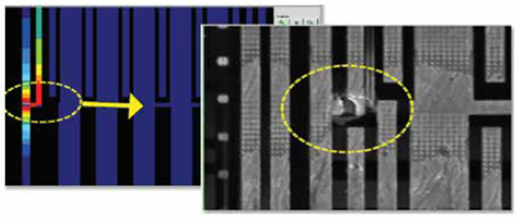

随着设计不断向5nm以及更先进的技术节点发展,片上互联的电迁移和静电放电问题会变得更为严峻。因此,鉴于电线中的电流不断增大,同时EM限值不断缩小,EM和ESD分析的准确度和覆盖范围就变得极为重要。

图5:在全芯片电源噪声仿真中使用RedHawk-CPA模型实现更高的结果准确性和粒度(来源:网络资源)

图6:准确预测电流值

图7:ESD引起的片上导线和ESD事件引起的过孔故障增加(摘自三星半导体公司Chan- hee Jeon等人的2013年国际ESD专题研讨会供稿:适用于鲁棒性I/O ESD网络设计的EOS/ESD电流强度分析方法)

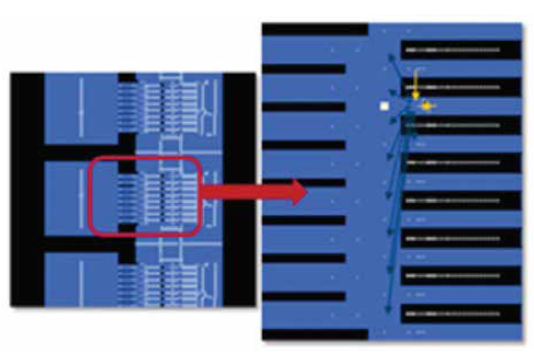

Ansys RedHawk-SC可为电源/接地和信号线路EM分析提供全面的支持。能在最大限度减少主动错误信息的同时,准确地对EM违规进行分析。专有的电流感知型提取方法有助于创建和仿真RLC网络,以便为设计中的每条电线和通孔实现签核质量的结果。作为RedHawk-SC平台的组成部分,Ansys PathFinder-SC™可为ESD事件中所有电流路径(电线和通孔)提供连接和互联失效检查,从而支持IP级到SoC级的ESD完整性分析。

用于电源噪声收敛的更大覆盖范围

对于采用高级工艺技术的设计而言,发现和解决因标准单元、内存、I/O和其它IP同步开关造成的电源噪声问题更显重要。通过使用全芯片瞬态仿真,RedHawk-SC可准确地预测同步开关输出产生的动态压降噪声。RedHawk-SC可将动态开关电流和电容模型与Totem提供的采用APL或CMM的晶体管级SPICE模型结合使用,从而生成SPICE级的准确结果。

图8:针对可靠性进行的温度感知型EM分析

为了能够更好地覆盖电源完整性和可靠性问题,即便是在缺少输入向量的时候,找出设计热点也非常关键。Ansys RedHawk-SC可支持VectorLess™动态仿真引擎,无论是否具有用户指定的全芯片验证范围约束条件,其均可自动生成开关情境。RedHawk-SC支持的其它无向量模式包括:PowerTransient™、FrequencyAware™以及VectorLess Scan等。

结果分析

RedHawk-SC功能齐备的多选项卡、多窗格GUI,实现同步显示各种不同的结果和表格,便于用户更好地展开分析与调试。这种基于布局的GUI,可为综合全面的易用型调试功能提供所需的灵活性和鲁棒性。多窗格GUI可提供多个芯片布局的视图,其中每个视图都可显示其功率密度以及相互之间的直接影响。通过使用这些多窗格配置,工程师能快速发现芯片上设计薄弱点的根本原因,然后找到并隔离能减少或消除压降或EM热点问题的修改办法。RedHawk-SC能够在 GUI环境中查看封装布线问题,并对其进行分析和调试。

图9:RTL到Silicon到system电源噪声收敛

可扩展生态系统的强大功能

Ansys电源噪声和可靠性生态系统,可从RedHawk-SC和其它相关的IC仿真平台进一步扩展,以包含下列成功投产的系统级仿真解决方案:Ansys SIwave™(信号完整性)、Ansys Icepak™(热完整性)和Ansys HFSS™ (EMI和高频分析)。借助这些业界标准的多物理场工具,用户能够使用系统感知型芯片仿真方法和芯片-封装感知型系统仿真方法,以确保芯片和系统在设计上能以最低成本协同工作。

总结

Ansys RedHaww-SC可实现多项全新的功能,并带有引擎增强的特性。对于使用高级工艺技术节点的设计,这些功能和特性不仅能实现更高的性能、更短的仿真周转时间,同时还能满足严格的签核要求。对于SoC电源噪声和可靠性分析而言,RedHawk-SC仍然是签核工具的不二选择。除了能够分析静态/动态压降和电源/信号线路EM签核以外,RedHawk-SC平台还能实现低功耗设计仿真、SoC ESD完整性验证、时序(时钟、关键路径)影响分析、电源网格原型构建以及芯片-封装-系统协同仿真。作为业界标准的签核工具,RedHawk-SC在最新的工艺节点上都取得了代工厂认证,包括台积电 (TSMC)基于3nm FinFET的工艺技术。RedHawk-SC获得了数千种成功投产芯片的青睐和支持。

(文章来源公众号:Ansys)

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

关于九游会J9电子

九游会J9电子技术有限公司(英文名称:Emdoor Electronics Technology Co.,Ltd)是国内资深的研发工具软件提供商,公司成立于 2002 年,面向中国广大的制造业客户提供研发、设计、管理过程中使用的各种软件开发工具,致力于帮助客户提高研发管理效率、缩短产品设计周期,提升产品可靠性。

20 年来,先后与 Altium、ARM、Ansys、QT、Adobe、Visu-IT、Minitab、Testplant、EPLAN、HighTec、GreenHills、PLS、Ashling、MSC Software 、Autodesk、Source Insight、TeamEDA、MicroFocus等多家全球知名公司建立战略合作伙伴关系,并作为他们在中国区的主要分销合作伙伴服务了数千家中国本土客户,为客户提供从芯片级开发工具、EDA 设计工具、软件编译以及测试工具、结构设计工具、仿真工具、电气设计工具、以及嵌入式 GUI 工具等等。九游会J9电子凭借多年的经验积累,真正的帮助客户实现了让研发更简单、更可靠、更高效的目标。

欢迎关注“九游会J9电子”公众号

了解更多研发工具软件知识

首页 > 新闻资讯

首页 > 新闻资讯

沪公网安备 44030602004326号

沪公网安备 44030602004326号