我们电子产品往往60%以上-可靠性方面的问题都出现在电子线路板的PCB设计上;工作及性能良好的PCB需要相关的理论及实践经验;我在产品的设计实践中经常碰到各种各样的问题;比如电子线路板不能通过系统EMS的测试标准,测试关键器件IC的功能引脚时出现高频噪声的问题,电路功能IC引脚检测到干扰噪声进行异常保护等等。

通过理论与实践结合;用测试数据检验我们的理论和实践的差异点!优良的设计跟长期的经验总结是密不可分的!

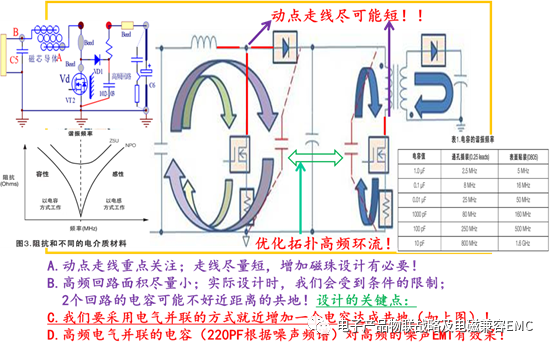

1. 开关电源通过以下的原理示意图分享设计总体原则

图示为我们常用的两种开关电源的拓扑结构;

A.开关电源拓扑主电流回流路径面积*小化;驱动脉冲电流回路*小化。

B.对于隔离开关电源拓扑结构,电流回路被变压器隔离成两个或多个回路(原边和副边),电流回路要分开*小回流面积布局布线设计。

C.如果电流回路有多个接地点,那么接地点要与中心接地点重合。

D.实际设计时,我们会受到条件的限制;如果2个回路的电容可能不好近距离的共地!

设计的关键点:

我们就要采用电气并联的方式就近增加一个高频电容达成共地(如图红色虚线)!

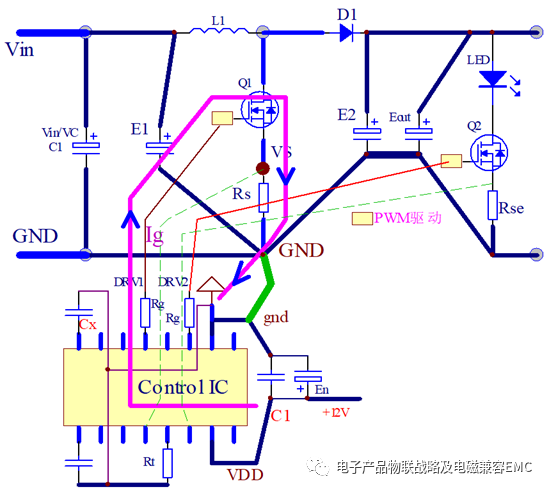

2.对于非隔离的IC控制器与主功率回路系统的PCB设计思路

如下图为-非隔离的电源给IC控制器供电,IC控制器控制LED的负载并进行调光及其它功能的控制应用。其控制器的供电及驱动回路的设计会影响系统的功能及可靠性。

通过图示IC控制器-PCB布局布线的设计思路如下:

A1.IC周边器件的地走线优先布局布线后连接到IC-gnd;

A2.IC-gnd再连接到滤波电容C1(高频电容-低容值)的接地端,如果是非隔离系统;存在主电源系统进行动态工作时,此地不再进行12V非隔离电源地连接。

A3.IC-控制中心的gnd要单点接地!C1电容靠近IC-gnd引脚,引脚地与C1电容-gnd*短连接。

关键环路

B.主电源回路路径的*小化设计原则

C.拓扑电流回路路径*小化设计原则

D.脉冲驱动回路路径*小化设计原则

注意条件受限时:电源的主回路与拓扑回路的电容可能不共地,我们可以采用电气并联的方式就近增加一个高频电容达成共地!

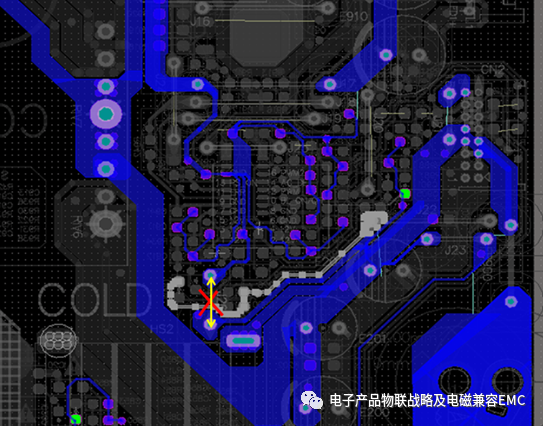

3.具体BOOST的LED驱动架构的PCB布局布线进行具体分析

设计基本思路如上所述;用下图进行设计分析

在图示中:黄色跳线(JX)有与12V回路地进行*小化环路面积的理论设计。

PCB蓝色高亮部分为系统GND走线,白色高亮部分为12V-IC供电电源正端走线。

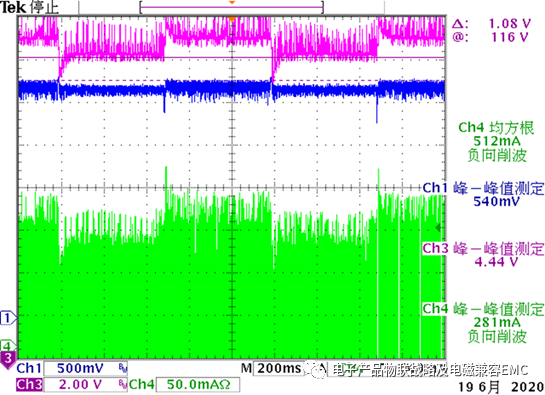

通过实际的数据测试验证黄色跳线(JX)连接线接地对系统的影响:

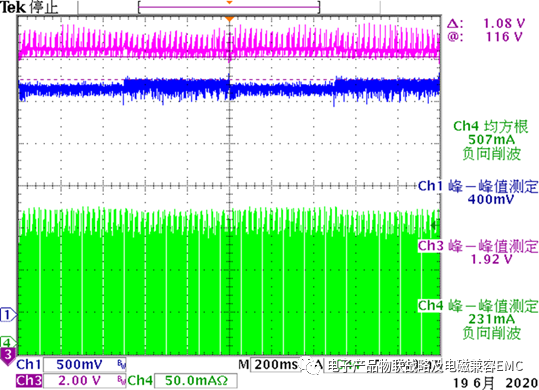

测试条件:12V-6A 115V/600mA (灯条)

测试项目:12V负载动态负载时间间隔500ms max load/minimum load6.6A/0.2A

示波器设置

CH1:12V(偏置10V) CH3:115V(偏置100V) CH4:ILED(偏置500mA)

黄色跳线(JX)在回路中:

黄色跳线(JX)去除

通过优化环路响应,增加动态响应速度。

黄色跳线(JX)的系统回路影响:

由于12V同时给控制IC提供VDD,在进行差分信号走线时12V与GND布线时即电源与地的回流面积*小;当12V拉负载时,12V电解电容正到地回流;当12V负载电流增加时地走线阻抗不等于0,这时在公共地阻抗上就会产生电压差,导致地基准位的变化。

去掉黄色跳线(JX)后,控制回路变成单点接地。此时地电位基准的影响就不受多个回路电流的影响。在非隔离的系统中单点接地符合设计理论。

设计经验总结:

可能存在多种原因,IC供电电源有多种应用功能连接。

A.对于隔离的控制器IC电路提供VDD,在进行差分信号走线时12V与GND布线时即电源与地的回流面积*小;

B.对于非隔离IC控制的GND要避免形成环路;IC同侧引脚的相同功能引脚的GND走线要连接在一起到IC-GND;IC-控制中心的gnd要求单点接地。。

关于九游会J9电子

九游会J9电子是国内综合的开发工具提供商, 致力于将全球先进的软件产品引荐给国内研发型企业使用,为企业提供研发、设计、管理过程中使用的各种软件工具,并致力于和客户一同提高研发、设计效率,缩短设计周期。九游会J9电子先后与arm、Altium、Ansys、QT、TestPlant、CollabNet、Parasoft以及TouchGFX等多家全球知名公司建立战略合作伙伴关系,并成为他们在中国区的重要分销合作伙伴。

九游会J9电子专注开发、设计、管理工具数十年,客户超过6000家,具有丰富的工具使用及客户支持经验积累,可以为客户提供从arm开发、EDA板级设计、软件编译及测试工具、结构设计工具、多物理场仿真工具以及嵌入式GUI工具等产品与服务。九游会J9电子在北京、上海、深圳设有分公司,业务遍布全国。

摘自维科网

首页 > 新闻资讯

首页 > 新闻资讯

沪公网安备 44030602004326号

沪公网安备 44030602004326号